il webcastインテル加速2021はiを明らかにしました2025年まで会社の計画競争に対応し、イノベーションの観点からもプロセッサセクターのガイダンスに戻ります。方向の変化は、アリゾナへの大規模な投資ですでに明らかであり、しばらく前までは減少する運命にあると思われる内部生産能力を明確に強化するように運命づけられていました。

しかし、今日、1つの目的がありますTSMCを使用したオープンチャレンジのインテル、最大のシリコンウェーハメーカー、トランジスタの内部生産における新しい米国政権からの資金調達などの要因、常に激しい競争に対処する必要性、あらゆる種類のPC市場の大成長に対処する必要性の組み合わせによって可能になったシナリオが可能になりました。とサイズ。

したがって、トランジスタのニュース、私を奪うまったく新しい命名法ナノメートル、アリゾナ州の200億の投資と、2024年の積み重ねられたチップから始まるIntelの創設者の顧客となるQualcomm Mobile Chip Giantとの契約では、Lake MeteorシリーズのようなIntel CPUに利益をもたらします。そしてだけでなく。

トランジスタの進化:FinfetからRebonfetへ

生産の問題を修正したIntelは、最終的に彼の巨大な財政を活用して、自分自身を再起動し、スタイリッシュにそれを行うことを決定しました。最も重要なイノベーションは、新しい第2世代のパッケージングフォーバーの到着に関係しています。これは、テクノロジーの進化から、チップの進化と実際のトランジスタへの投資に重要なテクノロジーをもたらすために設計された旅の最初のステップです。Finfetの到着まで新しいリボンフェットトランジスタ。しかし、Intel Foundry Services、したがって同社の鋳造所の潜在的な新しい顧客の観点から、Intel Siliconの品質を強調するように設計された命名法の変化を過小評価することはそうではありません。

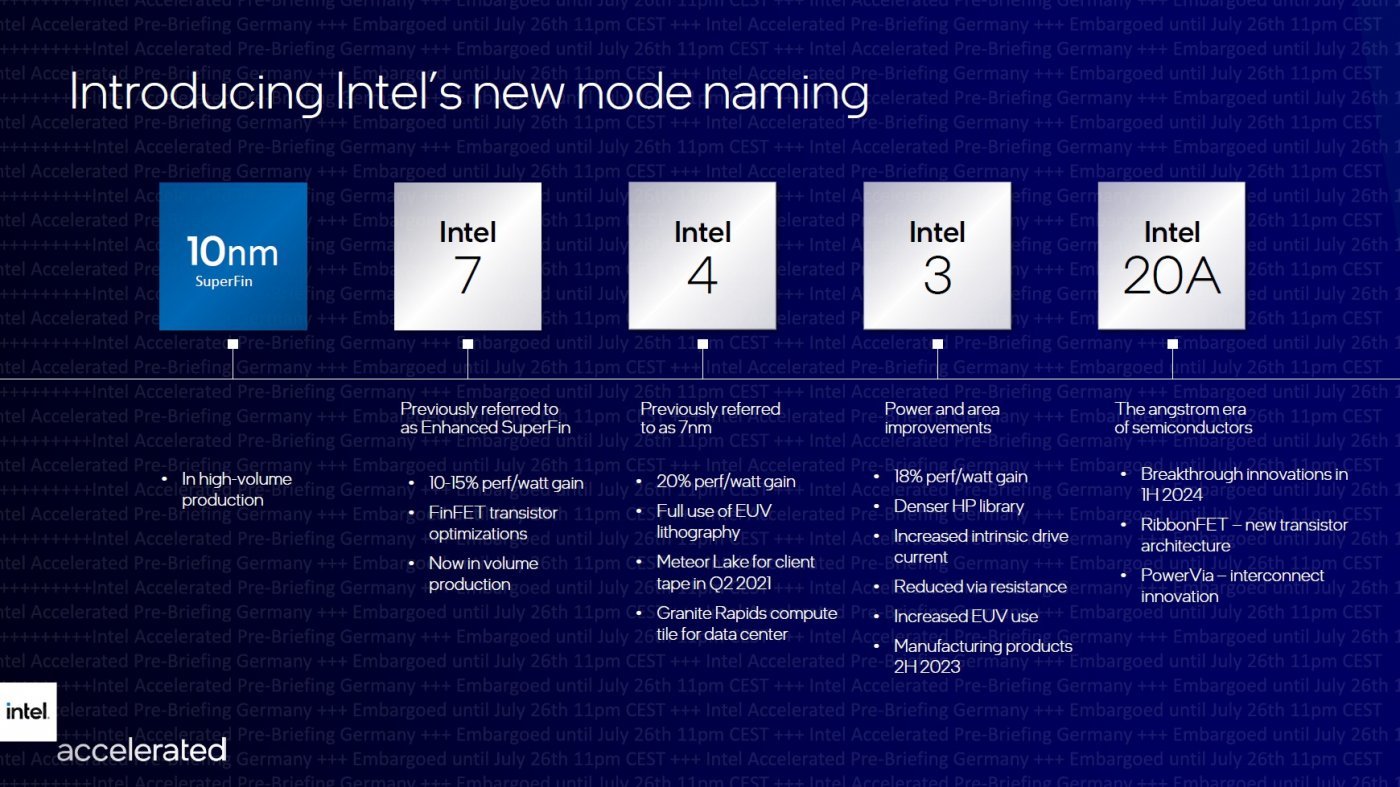

一方、トランジスタゲートの尺度は真実の一部のみを述べており、必ずしも効率と平方ミリメートルの密度が高いとは限りません。生産プロセスの削減は重要ですが、私たちはそれをよく知っています、私はトランジスタフィンフェット11世代のIntelコアプロセッサで使用される10ナノメートルでは、名前が正確にこれを示しているように見えるにもかかわらず、TSMCの7ナノメートルを持つものよりも後方ではなくなりました。したがって、サイズに基づいてクラシック名を脇に置き、新しい生産プロセスをより魅力的にし、Intel 7、Intel 4、Intel 3、Intel A20などの適切に認識できる名前を提供するというIntelの決定。後者の場合、トランジスタのサイズへの参照が戻りますが、オングストローム、ナノメートルの10分の1に対応する尺度。それでは、2024年に生産されるはずのチップについて2ナノメートルについて話しましょう。新しいトランジスタを使用し、このためにQualcommチップで使用されます。

とりわけ、IntelプランにはすでにIntel A18トランジスタが含まれているため、おそらくTSMCで事前にプレイする18Ångströmから、前述のIntel A20と同様の測定の観点から、2つのナノメートルトランジスタの設計にすでに取り組んでいます。しかし、私たちはそれを言った、数字はチップについてすべてを言っているわけではない。 3次元トランジスタへの移行により、密度はゲートの単純な測定から放出されているため、10ナノメートルチップ強化スーパーフィンは、生産プロセスに基づいて7ナノメートルのナノメートルのナノメートルまでのチップよりも多くのトランジスタを持つことができます。 TSMC。そして、それはIntelがIntel 7を放棄することを強調したかったものであり、TSMCへの直接的な課題を開始する意図を繰り返し繰り返した動きで。

だからここにありますIntelプロセッサは2025年までロードマップします、新しい命名法で。

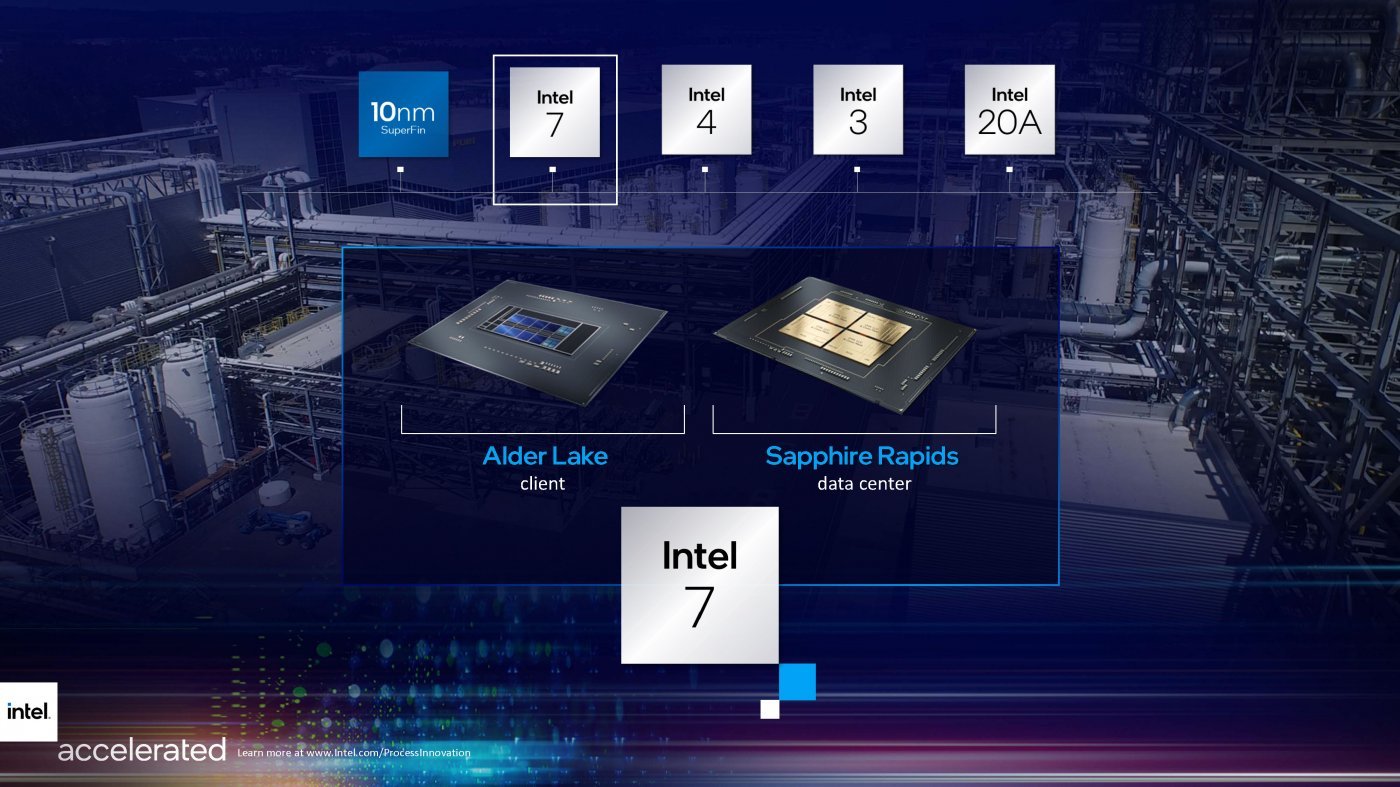

Intel 7

生産プロセス10ナノメートルは、現在呼ばれているスーパーフィンを強化しましたIntel 7これは、新しいLGA1700ソケットとともに年末に到着する差し迫ったアルダーレイクハイブリッドプロセッサに使用されているものであり、Intelによれば、10%から10%までのサイザーに含まれるWATTパフォーマンスの増加を保証することができます。トランジスタ10 nmスーパーフィンと比較して15%。これは、2022年第1四半期から生産されるデータセンターサファイアラピッズプロセッサにもIntelがテクノロジーを使用できるようにするため、Finfetトランジスタの最適化のおかげです。

Intel 4

Intel 4、以前は7つのナノメートルの生産プロセスであることを目的としていたため、EUVリソグラフィを使用します。これは、トランジスタFinfetと組み合わせて、1平方ミリメートルあたり200〜2億5,000万のトランジスタを凝縮できます。したがって、5 TSMCナノメートルを超えるはずであり、4番目のトランジスタで停止し、実際の行為でさえ見たいと思う優位性を指摘するために4番の選択で表されるように。

一方、トランジスタは10年前に開発されたIntel Finfetであると述べています。しかし、最適化と新しい生産プロセスの間で、ワットとパフォーマンスの比率の点でさらに20%増加することを保証する必要があります。生産は2022年に開始され、最初の製品は2023年に到着し、デスクトップと高性能ノートブックのインテルメテオレイクのプロセッサから始まり、その後、データセンターグラナイトラピッズのCPUが続き、新世代のパッケージングFOVEROSも利用します。したがって、彼らは効率性の点で明確な飛躍を遂げることができました。

Intel 3

またIntel 3Finfetトランジスタの最適化に焦点を当てますが、EUVリソグラフィーの解像度の増加と生産プロセスへの増加と組み合わされます。これは、少なくともトランジスタの観点から、名前が予想されるように、TSMCの3つのナノメートルに匹敵するはずです。 1ミリ四方あたりの密度。この場合、この場合、消費とパフォーマンスの比率が18%の比率の増加であり、2023年の生産の開始を考慮して、デスクトップとIntelのノートブックプロセッサを使用して、まだ名前が付いていません。 2024年の到着。

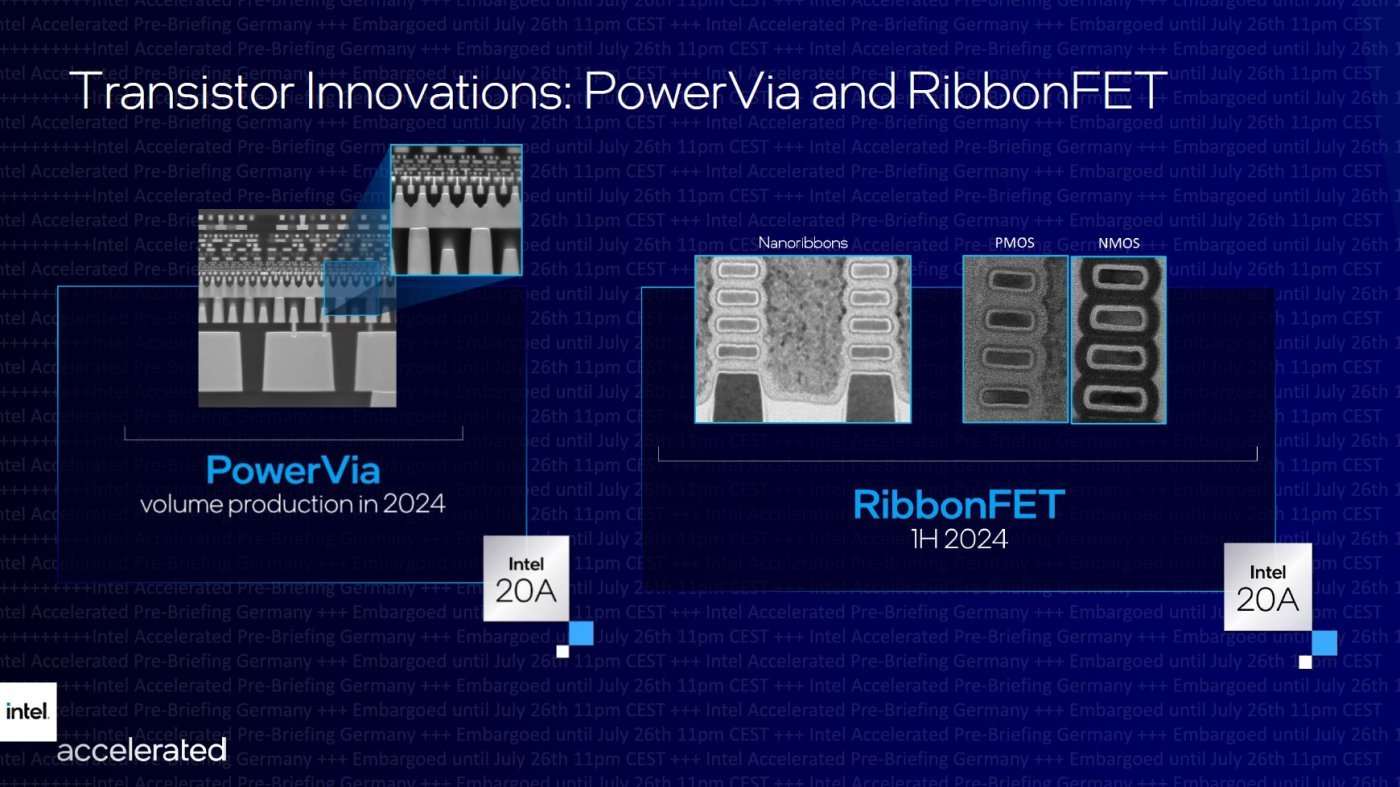

Intel 20a

トランジスタの到着Intel 20a生産への参入が2024年に予定されているため、顧客に対するIntel Foundryサービスの魅力的性のために、将来のIntelプロセッサにとって非常に重要です。しかし、3年で物事は根本的に変化する可能性がありますが、彼らはすでに完全に新しいテクノロジーの導入を利用することを誰が利用するだろうと確信しているようです。 13年間の名誉あるキャリアの後、Finfetトランジスタは最終的に本当に素晴らしいことを約束するリボンフェットに置き換えられます。

まず、すべての側面のゲートについて話します。同じアクティベーション電流に対する電流ゲートのスイッチング速度よりも高いことを約束し、変数のあるトランジスタを生成できる垂直フィンの使用により、サイズが低い幅。しかし、それ以上ありますPowerviaテクノロジーこれは、プロセッサの分野で常に問題を引き起こしてきた大きなボトルネックの問題を解決することを約束します。 Intelの解決策は、与えられた相互接続を電気コンポーネントから分離することであり、後者はトランジスタのベースに配置され、したがって電源と直接接触し、強度と信号洗浄電気の観点からケースのすべての利点を伴いました。

Intel 18a

ロードマップインテルには、生産プロセスの年である2025も含まれていますIntel 18aこれは、おそらく2026年にリボンフェットトランジスタをさらに精製し、生産プロセスのサイズをさらに10%削減するために、実際のプロセッサに変わるでしょう。これは、創業者をあらゆる顧客にとってさらに魅力的にすることを目的とした新しい高NA EUVリソグラフィのおかげです。そうするために、彼はそれぞれ最大1億2,000万ドルかかる可能性のあるスキャナーを利用できる極端な紫外線リソグラフィのリーダーであるASMLと協力することを決めたのは偶然ではありません。

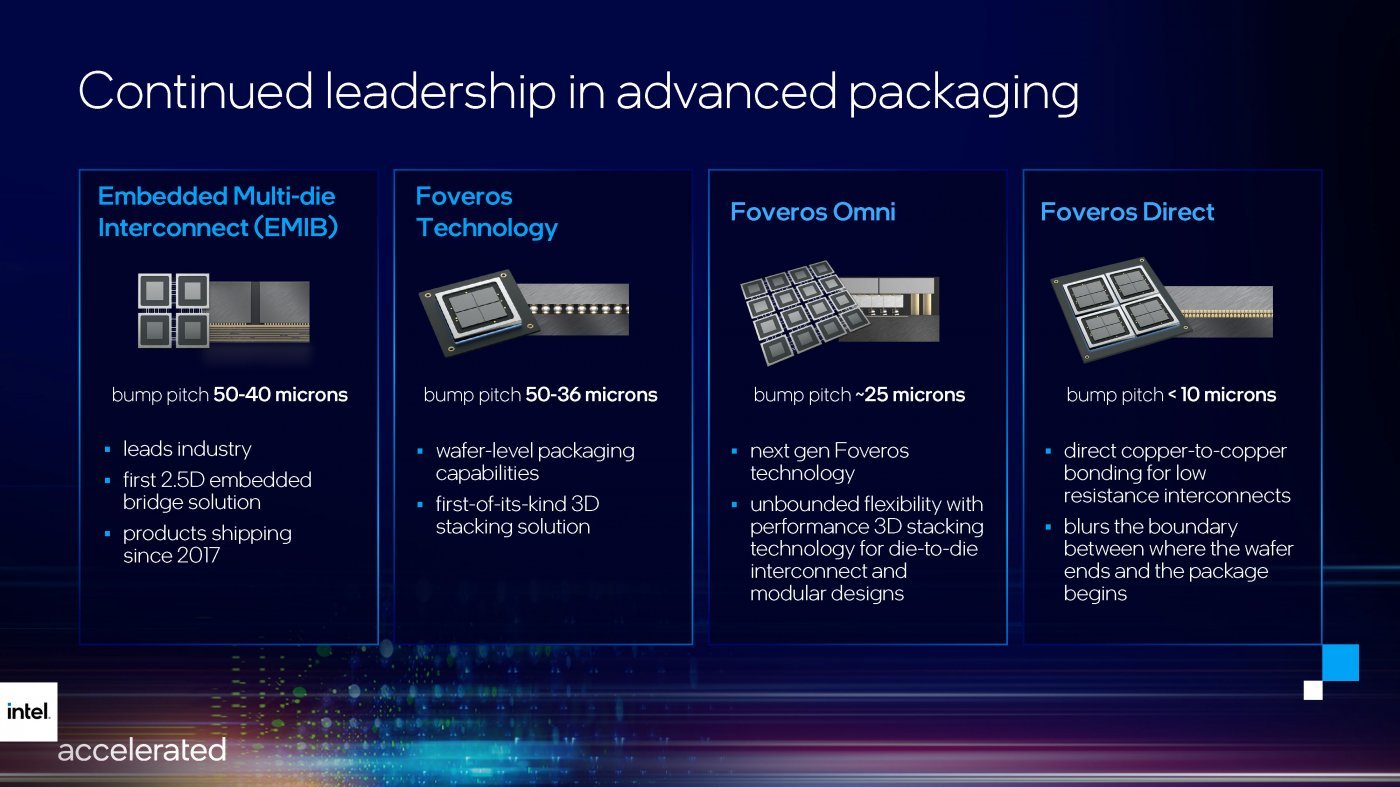

FOVEROS:プロセッサの変換

パッケージングテクノロジーは、プロセッサを含むパッケージングとは何の関係もありませんが、データの送信、寸法、および寸法の面で利点を得るために、チップのさまざまなコンポーネントが組み合わされる方法に関係しています。効率。の最初の化身foverosCPU、GPU、およびメモリが同じダイで積み重ねられているレイクフィールドプロセッサと一緒に仕事をしているのをすでに見ていますが、2023年に到着するデスクトッププロセッサとIntel Meteor Lakeノートブックのタイルで使用されています。電力マージンとバンプピッチの観点から、第2世代のフォーバーの改善を利用して、わずか36ミクロンに減少します。

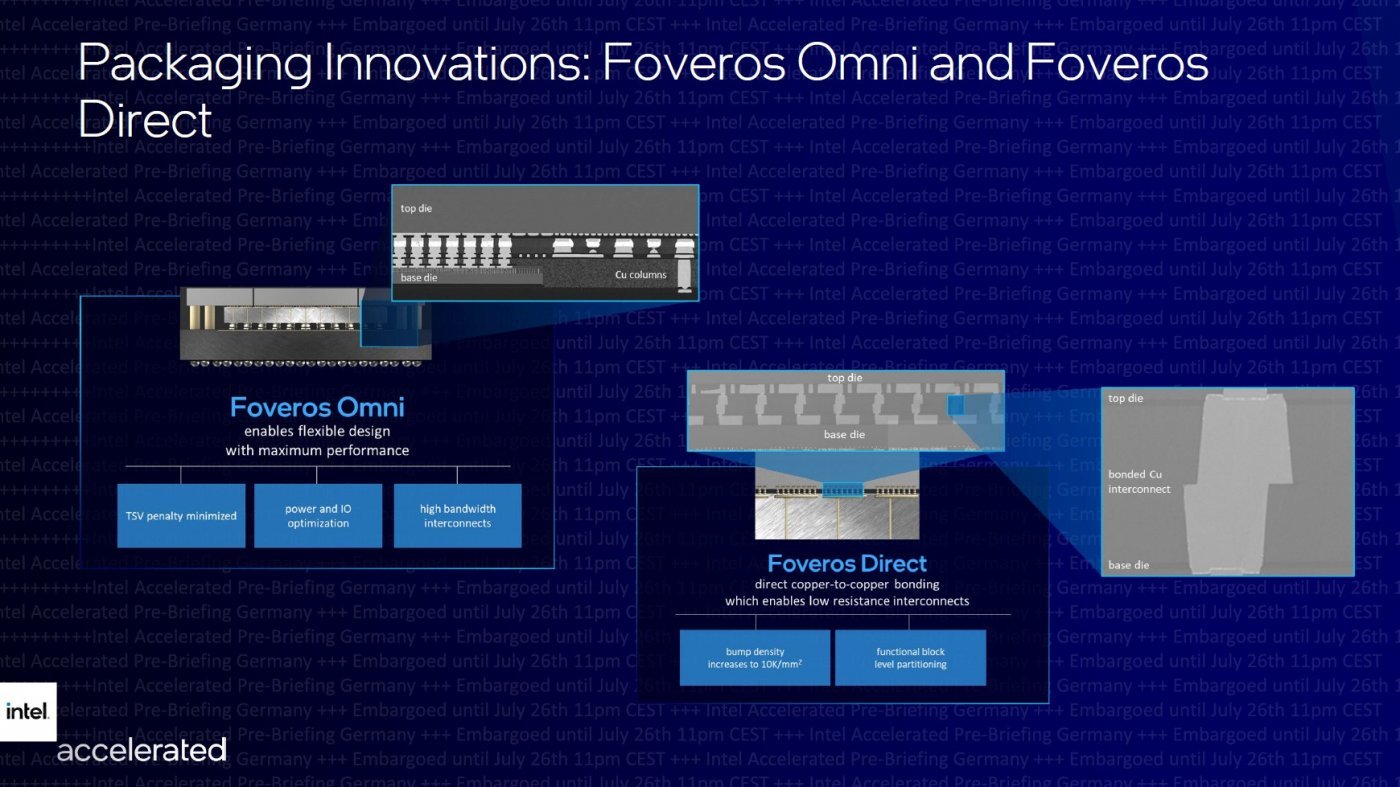

FOVEROS OMNI

私たちは、モノリシックチップのパフォーマンスにますます近い相互接続速度について話しています。FOVEROS OMNI。一方、2023年から利用可能であるため、2023年に来るIntelチップを特徴付けるこの第3世代は、さまざまな生産プロセスに基づいてスタッキングレイヤーの可能性を導入し、開発段階と中でほぼ絶対的な柔軟性を提供します。任意のシステムにインストールされているチップのエネルギー管理。すべては、故障したレイヤーがパイル全体を台無しにするのを防ぐために、チップの個々のコンポーネントの動作を検証できるようにするために、ダイーダイの相互接続によって濃縮されます。

Foveros Direct

Foveros Omniと一緒に到着しますFoveros Directこれにより、銅から銅への直接的な相互接続が実装され、全体的な密度が明らかに大きくなり、バンプピッチは10ミクロン未満で、抵抗性の低下と効率の増加という点で指数関数的な利点を保証するはずです。したがって、それはインテルの兵器庫にあるもう1つの基本的な武器になります。 CPUの歴史を作り、まだそれをやりたいと思っています。

実際、消費者分野だけでなく、EMIBの相互接続の進化と、少なくともTSMCと競合できる唯一の鋳造所の役割でサーバー市場にも主人公を見るこのトリプルソウルがあります。非常に高解像度の高NA EUVリソグラフィのような未来のテクノロジーの正面。

ただし、最初に、ハイブリッドコアプロセッサへの飛躍があります。これは、サンフランシスコの10月27日と28日に予定されているIntel Innovationイベントの主人公の1つであるIntel Alder Lakeシリーズの1つであることになります。